#### **Performance Characteristics**

• -Frequency Range: 8GHz - 12GHz;

• Receive Gain: 22dB;

• Noise Figure: 3dB;

• - Transmit Power Gain: 28dB:

• - Transmit Saturation Power: 37dBm;

• - 6-bit Phase Shifter RMS: 5°;

• - 6-bit Attenuator RMS : 1.2dB:

• - TTL-level Serial Control;

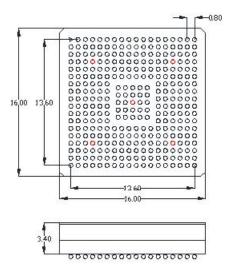

Module Size: 16mm×16mm×3.4mm (excluding balls);

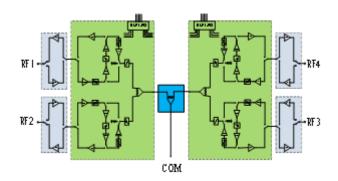

#### **Principle Block Diagram**

#### **Product Introduction**

**Electrical Parameters**

HX9X4010G16 is an X-band surface-mount four-channel transceiver module. It adopts the BGA packaging form. The shell is made of ceramic substrate, and the enclosure and cover are made of metal materials. The thermal resistance of the module is reduced by means of heat dissipation from the top and the bottom simultaneously. The module integrates the following circuit functions: 6-bit numerically controlled phase shifter, 6-bit attenuator, transmit driver amplifier, receive low-noise amplifier, power divider, switch circuit, and serial-to-parallel driver, etc. The operating frequency ranges from 8GHz to 12GHz. The receive gain is 20dB, the noise figure is 3dB, the transmit output saturation power is 37dBm, and the transmit power gain is 28dB. This module is mainly applied to microwave transceiver components to achieve functions such as amplification, amplitude modulation, and phase modulation of transceiver signals.

When the transmit channel and the receive channel are working, Vd1 = +28V, Vd2 = +3.3V, Vee1=-5V, Vee2=-28V. The following are the single-channel indicate:

| Parameter | Parameter      | Test Conditions   | Minimum | Typical | Maximum | Unit |

|-----------|----------------|-------------------|---------|---------|---------|------|

| Name      | Name           | Pulse Width 50us  | Value   | Value   | Value   |      |

|           |                | Duty Cycle 5% f = |         |         |         |      |

|           |                | 8 -12GHz          |         |         |         |      |

| Transmit  | Transmit Gain  | TA = 25°C         | -       | 28      | -       | dB   |

| Channel   |                |                   |         |         |         |      |

|           | Gain Flatness  | TA = 25°C         | -1      | -       | 1       | dB   |

|           |                |                   |         |         |         |      |

|           | Saturation     | TA = 25°C         | -       | 37      | -       | dBm  |

|           | Power          |                   |         |         |         |      |

|           | Input Port     | TA = 25°C         | -       | 1.5     | -       |      |

|           | VSWR           |                   |         |         |         |      |

|           | Number of      | TA = 25°C         | 6bit,   | 6bit,   | 6bit,   |      |

|           | Phase Shifting |                   | 5.625°  | 5.625°  | 5.625°  |      |

|           | Bits           |                   |         |         |         |      |

|                    | RMS of              | TA = 25°C |        | 5      |        | 0   |

|--------------------|---------------------|-----------|--------|--------|--------|-----|

|                    |                     | 1A - 25°C | _      | 3      | -      |     |

|                    | 64-phase            |           |        |        |        |     |

|                    | Shifting States     | T. 250G   | 1      |        | 1      | 100 |

|                    | Phase Shifting      | TA = 25°C | -1     | -      | 1      | dB  |

|                    | Amplitude           |           |        |        |        |     |

|                    | Variation           |           |        |        |        |     |

|                    | Channel Gain        | TA = 25°C | -0.5   | -      | 0.5    | dB  |

|                    | Consistency         |           |        |        |        |     |

|                    | Channel Phase       | TA = 25°C | -30    | -      | 30     | 0   |

|                    | Consistency         |           |        |        |        |     |

|                    | VD1 Current         | TA = 25°C | -      | 650    | -      | mA  |

|                    | VD2 Current         | TA = 25°C | -      | 350    | -      | mA  |

|                    | Veel Current        | TA = 25°C | -      | 1.5    | -      | mA  |

| Receive<br>Channel | Noise Figure        | TA = 25°C | -      | 3.0    | -      | dB  |

|                    | Receive Gain        | TA = 25°C | -      | 22     | -      | dB  |

|                    | Gain Flatness       | TA = 25°C | -1     | -      | 1      | dB  |

|                    | Input P-1           | TA = 25°C | -      | -27    | -      | dBm |

|                    | Input Port<br>VSWR  | TA = 25°C | -      | 1.3    | -      |     |

|                    | Number of           | TA = 25°C | 6bit,  | 6bit,  | 6bit,  |     |

|                    | Phase Shifting Bits |           | 5.625° | 5.625° | 5.625° |     |

|                    | RMS of              | TA = 25°C | -      | 2.5    | -      | 0   |

|                    | 64-phase            |           |        |        |        |     |

|                    | Shifting States     |           |        |        |        |     |

|                    | Phase Shifting      | TA = 25°C | -1.5   | -      | 1.5    | dB  |

|                    | Amplitude           |           |        |        |        |     |

|                    | Variation           |           |        |        |        |     |

|                    | Number of           | TA = 25°C | 6 bit, | 6 bit, | 6 bit, |     |

|                    | Attenuation         |           | 0.5dB  | 0.5dB  | 0.5dB  |     |

|                    | Bits                |           |        |        |        |     |

|                    | RMS of 64           | TA = 25°C | _      | 1      | _      | dB  |

|                    | Attenuation         |           |        | _      |        |     |

|                    | States              |           |        |        |        |     |

|                    | Additional          | TA = 25°C | -10    | _      | 10     | 0   |

|                    | Phase Shift of      |           |        |        |        |     |

|                    | Attenuation         |           |        |        |        |     |

|                    |                     | 1         |        | 1      |        |     |

| Channel Gain  | TA = 25°C | -1  | -   | 1  | dB |

|---------------|-----------|-----|-----|----|----|

| Consistency   |           |     |     |    |    |

| Channel Phase | TA = 25°C | -30 | -   | 30 | 0  |

| Consistency   |           |     |     |    |    |

| Vd1 Current   | TA = 25°C | -   | 0   | -  | mA |

|               |           |     |     |    |    |

| Vd2 Current   | TA = 25°C | -   | 95  | -  | mA |

|               |           |     |     |    |    |

| Vee1 Current  | TA = 25°C | -   | 1.5 | -  | mA |

|               |           |     |     |    |    |

## **Operating Limit Parameters**

| Parameter                                | Symbol          | Limit Value    |  |  |

|------------------------------------------|-----------------|----------------|--|--|

| Maximum Drain-Source<br>Voltage 1        | Vd1             | +32V           |  |  |

| Maximum Drain-Source<br>Voltage 2        | Vd2             | +4V            |  |  |

| Minimum Driver Supply Voltage            | Vee             | -5.5V          |  |  |

| Maximum Input Power<br>(RF1/RF2/RF3/RF4) | Pin(200us, 20%) | +40dBm         |  |  |

| Maximum Input Power (COM)                | Pin             | +15dBm         |  |  |

| Storage Temperature                      | TSTG            | -55°C to +85°C |  |  |

| Operating Temperature                    | Тор             | -55°C to +85°C |  |  |

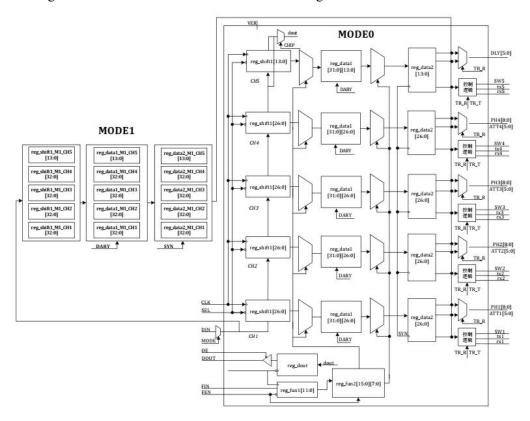

Registers in the beam control circuit can be classified into five categories according to their functions, as shown in the following table:

|                    | Register  |           | Name                      | Definition                                                                                                              |

|--------------------|-----------|-----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Register<br>Status | reg_shift |           | Status Shift<br>Register  | Shift register, containing amplitude - phase and transmit - receive control data for each channel                       |

|                    | reg_data  | reg_data1 | Status Data<br>Register 1 | The first - stage latch, with 32 sets of registers for each channel. The read - write address is determined by reg_fun2 |

|                     |          | reg_data2 | Status Data<br>Register 2    | The second - stage latch                                                     |

|---------------------|----------|-----------|------------------------------|------------------------------------------------------------------------------|

| Register<br>Control | reg_fun1 |           | Control<br>Shift<br>Register | Shift register, writing the read - write address bit data of reg_data1       |

|                     | reg_fun2 |           | Control Data<br>Register     | Stores the read - write address data of reg_data1, with 16 sets of registers |

### **Definition of the Control Register Structure**

There are 16 control data registers (reg\_fun2), and each register contains 8 - bit data, as shown in the following table. Only the lower 5 - bit of the first two control data registers are used in this protocol, corresponding to the write and read addresses of the status data register 1 (reg\_data1) respectively.

| reg_fun2           | D7 | D6                  | D5 | D4 | D3    | D2    | D1     | D0                          | Explanation |  |  |

|--------------------|----|---------------------|----|----|-------|-------|--------|-----------------------------|-------------|--|--|

| reg_fun2[0]        | -  | -                   | -  |    | reg2_ | addr_ | w[4:0] | Write address bit selection |             |  |  |

| reg_fun2[1]        | -  | -                   | -  |    | reg2_ | addr  | r[4:0] | Read address bit selection  |             |  |  |

| reg_fun2[2] - [15] |    | Internally reserved |    |    |       |       |        |                             |             |  |  |

The control shift register (reg\_fun1) contains read - write address bit control signals. reg\_fun1 contains 12 - bit data, where addr is the high 4 - bit of reg\_fun1, representing the address of the control data register (reg\_fun2), and data is the low 8 - bit of reg\_fun1, representing the data written into the corresponding reg\_fun2.

| Control Shift Register | 11 |      | 8 | 7 |      | 0 |

|------------------------|----|------|---|---|------|---|

| Content<br>Definition  |    | addr |   |   | data |   |

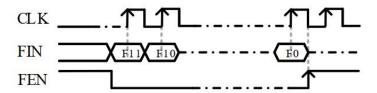

When configuring the control register, when FEN is at a low level, on the rising edge of CLK, the FIN input signal will be sequentially written into reg fun1[0], and the original data in

reg\_fun1 will be sequentially shifted from reg\_fun1[0] to reg\_fun1[11]. reg\_fun1 will write the data in data into the specified position in reg\_fun2 according to the value of addr. For example, when addr is 0x1, data will be written into reg\_fun2[1].

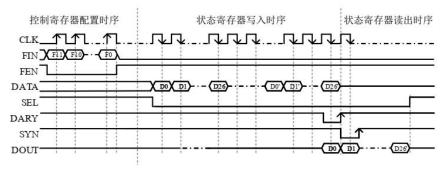

The basic functions of the SPI interface protocol rely on eight interfaces: CLK, SEL, DATA, DARY, SYN, DOUT, FIN, and FEN. CLK is the system synchronization clock, FIN is the serial input signal of the control shift register, and FEN is a low - level - effective enable signal. When FEN is low, on the rising edge of CLK, the FIN serial input signal is stored in the control shift register (reg\_fun1) until all 12 - bit signals are stored. At this time, the FEN signal is pulled high, and on the first rising edge of CLK after being pulled high, the 12 - bit data is written into the control data register (reg\_fun2). The write timing diagram of the control register is as follows:

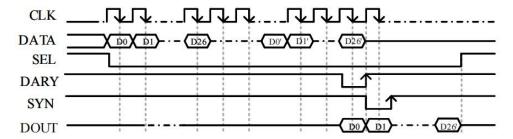

SEL is a low - level - effective chip select synchronization signal, DATA is the serial input signal of the status shift register (reg\_shift), and DOUT is the serial output signal of the status shift register (reg\_shift). The input of DATA and the output of DOUT are both at the falling edge of CLK when SEL is at a low level, and the writing and output are in groups of the complete data of all channels. When the SEL signal changes from high to low, the chip is selected, and the serial input signal of DATA starts to be stored in the status shift register until all signals are stored. At this time, DOUT starts to output the first - bit serial input signal.

After the DATA data is written, on the rising edge of DARY, the serial data is written into the status data register 1 (reg\_data1), and the write address bit of reg\_data1 is determined by the control data register (reg\_fun2). On the rising edge of SYN, the data in reg\_data1 is read out to the status data register 2 (reg\_data2), and the read address bit of reg\_data1 is determined by reg\_fun2. After the data is output through reg\_data2, it passes through a multiplexer with TR\_R as the selection signal to output the transmit - receive amplitude - phase and switch control signals. The write and read timing of the status register is as follows. It should be noted that the serial write operation after power - on should be completed after the power - on reset delay (between 20 - 60us).

Block Diagram of the Beam Control Circuit is as following:

- 1. reg\_shift1\_CHx (x = 1 4) is the status shift register. At the falling edge of CLK, if SEL is 0, the shift starts. The data enters reg\_shift1\_CH1 from the DATA port and starts to shift. The data in reg\_shift1\_CH1[26] starts to shift towards reg\_shift1\_CH1[0], and the value of reg\_shift1\_CH1[0] is shifted to reg\_shift1\_CH2[26] (that is, the first input data is the lowest bit reg\_shift1\_CH5[0] of channel 5), and the same rule applies to channels 2, 3, 4, and 5.

- 2. reg\_data1\_CHx (x = 1 4) is the status data register 1, corresponding to the previous stage reg\_shift1\_CHx respectively. Each channel's reg\_data1\_CHx has 32 sets of registers, namely reg\_data1\_CHx[31] reg\_data1\_CHx[0]. On the rising edge of DARY, all the data in reg\_shift1\_CHx will be written into reg\_data1\_CHx specified by reg\_fun2[0][4:0].

- 3. reg\_data2\_CHx (x = 1 4) is the status data register 2, corresponding to the previous stage reg\_shift1\_CHx and reg\_data1\_CHx respectively. On the rising edge of SYN, the data selected by reg\_fun2[1][4:0] in reg\_data1\_CHx will be read out to reg\_data2\_CHx.

4. After the data is output through reg\_data2\_CHx, it passes through a multiplexer with TR\_R as the selection signal to output the transmit - receive amplitude - phase and switch control signals.

Timing Diagram of Function Register Configuration

The single - read - write control timing diagram is as shown above.

- 1. First configure the read write address bits in the control register.

- 2. When configuring the control register, pull the SEL signal high; when configuring the status register, pull the FEN signal high to avoid data misalignment or incorrect storage.

#### **Truth Table**

The module's serial data has 122 bits. In the module, each of channels 1 - 4 has 27 bits, and the common channel has 14 bits. The function definitions of the data bits are shown in the following table.

| Delay | Delay  | Chan  | Channel 4   | Cha | Channel  | Chan  | Channel  | Chan  | Channel  |

|-------|--------|-------|-------------|-----|----------|-------|----------|-------|----------|

| Chan  | Chann  | nel 4 |             | nne | 3        | nel 2 | 2        | nel 1 | 1        |

| nel   | el     |       |             | 13  |          |       |          |       |          |

| D0    | Receiv | D14   | Receive     | D4  | Receive  | D68   | Receive  | D95   | Receive  |

|       | e      |       | Enable      | 1   | Enable   |       | Enable   |       | Enable   |

|       | Enable |       | Control Bit |     | Control  |       | Control  |       | Control  |

|       | Contro |       |             |     | Bit      |       | Bit      |       | Bit      |

|       | 1 Bit  |       |             |     |          |       |          |       |          |

| D1    | Trans  | D15   | Transmit    | D4  | Transmit | D69   | Transmit | D96   | Transmit |

|       | mit    |       | Enable      | 2   | Enable   |       | Enable   |       | Enable   |

|       | Enable |       | Control Bit |     | Control  |       | Control  |       | Control  |

|       | Contro |       |             |     | Bit      |       | Bit      |       | Bit      |

|       | 1 Bit  |       |             |     |          |       |          |       |          |

| D2    | Set to | D16   | Set to 0    | D4  | Set to 0 | D70   | Set to 0 | D97   | Set to 0 |

|       | 0      |       |             | 3   |          |       |          |       |          |

| D3    | Set to | D17   | Transmit    | D4  | Transmit | D71   | Transmit | D98   | Transmit |

|       | 0      |       | Phase Shift | 4   | Phase    |       | Phase    |       | Phase    |

|       |        |       | Control Bit |     | Shift    |       | Shift    |       | Shift    |

|       |        |       | 5.625°      |     | Control  |       | Control  |       | Control  |

|                |        |     |                 |           | Bit       |         | Bit       |       | Bit       |

|----------------|--------|-----|-----------------|-----------|-----------|---------|-----------|-------|-----------|

|                |        |     |                 |           | 5.625°    |         | 5.625°    |       | 5.625°    |

| D4             | Set to | D18 | Transmit        | D4        | Transmit  | D72     | Transmit  | D99   | Transmit  |

| D <del>4</del> | 0      | ועם | Phase Shift     | 5         | Phase     | D/2     | Phase     | D99   | Phase     |

|                | 0      |     | Control Bit     | 3         | Shift     |         | Shift     |       | Shift     |

|                |        |     | 11.25°          |           | Control   |         | Control   |       | Control   |

|                |        |     | 11.23           |           | Bit       |         | Bit       |       | Bit       |

|                |        |     |                 |           | 11.25°    |         | 11.25°    |       | 11.25°    |

| D5             | Set to | D19 | Transmit        | D4        | Transmit  | D73     | Transmit  | D100  | Transmit  |

| D3             | 0      | D19 | Phase Shift     | 6         | Phase     | טון און | Phase     | D100  | Phase     |

|                | 0      |     | Control Bit     | 0         | Shift     |         | Shift     |       | Shift     |

|                |        |     | 22.5°           |           | Control   |         | Control   |       | Control   |

|                |        |     | 22.3            |           | Bit 22.5° |         | Bit 22.5° |       | Bit 22.5° |

| D6             | Set to | D20 | Transmit        | D4        | Transmit  | D74     | Transmit  | D101  | Transmit  |

| Do             |        | D20 | Phase Shift     | D4<br>  7 | Phase     | D/4     | Phase     | וטוטו | Phase     |

|                | 0      |     |                 | '         |           |         |           |       |           |

|                |        |     | Control Bit 45° |           | Shift     |         | Shift     |       | Shift     |

|                |        |     | 43              |           | Control   |         | Control   |       | Control   |

| D7             | G 4 4  | D21 | T '4            | D4        | Bit 45°   | D75     | Bit 45°   | D102  | Bit 45°   |

| D7             | Set to | D21 | Transmit        | D4        | Transmit  | D75     | Transmit  | D102  | Transmit  |

|                | 0      |     | Phase Shift     | 8         | Phase     |         | Phase     |       | Phase     |

|                |        |     | Control Bit     |           | Shift     |         | Shift     |       | Shift     |

|                |        |     | 90°             |           | Control   |         | Control   |       | Control   |

| Do             | G 4 4  | Daa | т :             | D4        | Bit 90°   | D76     | Bit 90°   | D102  | Bit 90°   |

| D8             | Set to | D22 | Transmit        | D4        | Transmit  | D76     | Transmit  | D103  | Transmit  |

|                | 0      |     | Phase Shift     | 9         | Phase     |         | Phase     |       | Phase     |

|                |        |     | Control Bit     |           | Shift     |         | Shift     |       | Shift     |

|                |        |     | 180°            |           | Control   |         | Control   |       | Control   |

| D.O.           |        | D22 |                 | D.#       | Bit 180°  | D.55    | Bit 180°  | D104  | Bit 180°  |

| D9             | Set to | D23 | Receive         | D5        | Receive   | D77     | Receive   | D104  | Receive   |

|                | 0      |     | Phase Shift     | 0         | Phase     |         | Phase     |       | Phase     |

|                |        |     | Control Bit     |           | Shift     |         | Shift     |       | Shift     |

|                |        |     | 5.625°          |           | Control   |         | Control   |       | Control   |

|                |        |     |                 |           | Bit       |         | Bit       |       | Bit       |

|                |        |     |                 |           | 5.625°    |         | 5.625°    |       | 5.625°    |

| D10            | Set to | D24 | Receive         | D5        | Receive   | D78     | Receive   | D105  | Receive   |

|                | 0      |     | Phase Shift     | 1         | Phase     |         | Phase     |       | Phase     |

|                |        |     | Control Bit     |           | Shift     |         | Shift     |       | Shift     |

|                |        |     | 11.25°          |           | Control   |         | Control   |       | Control   |

|                |        |     |                 |           | Bit       |         | Bit       |       | Bit       |

|                |        |     |                 |           | 11.25°    |         | 11.25°    |       | 11.25°    |

| D11            | Set to | D25 | Receive         | D5        | Receive   | D79     | Receive   | D106  | Receive   |

|                | 0      |     | Phase Shift     | 2         | Phase     |         | Phase     |       | Phase     |

|                |        |     | Control Bit     |           | Shift     |         | Shift     |       | Shift     |

|     |        |     | 22.5°       |    | Control   |     | Control   |      | Control   |

|-----|--------|-----|-------------|----|-----------|-----|-----------|------|-----------|

|     |        |     | 22.5        |    | Bit 22.5° |     | Bit 22.5° |      | Bit 22.5° |

| D12 | Set to | D26 | Receive     | D5 | Receive   | D80 | Receive   | D107 | Receive   |

|     | 0      |     | Phase Shift | 3  | Phase     |     | Phase     |      | Phase     |

|     |        |     | Control Bit |    | Shift     |     | Shift     |      | Shift     |

|     |        |     | 45°         |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 45°   |     | Bit 45°   |      | Bit 45°   |

| D13 | Set to | D27 | Receive     | D5 | Receive   | D81 | Receive   | D108 | Receive   |

|     | 0      |     | Phase Shift | 4  | Phase     |     | Phase     |      | Phase     |

|     |        |     | Control Bit |    | Shift     |     | Shift     |      | Shift     |

|     |        |     | 90°         |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 90°   |     | Bit 90°   |      | Bit 90°   |

|     |        | D28 | Receive     | D5 | Receive   | D82 | Receive   | D109 | Receive   |

|     |        |     | Phase Shift | 5  | Phase     |     | Phase     |      | Phase     |

|     |        |     | Control Bit |    | Shift     |     | Shift     |      | Shift     |

|     |        |     | 180°        |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 180°  |     | Bit 180°  |      | Bit 180°  |

|     |        | D29 | Transmit    | D5 | Transmit  | D83 | Transmit  | D110 | Transmit  |

|     |        |     | Attenuatio  | 6  | Attenuat  |     | Attenuat  |      | Attenuat  |

|     |        |     | n Control   |    | ion       |     | ion       |      | ion       |

|     |        |     | Bit 0.5dB   |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit       |     | Bit       |      | Bit       |

|     |        |     |             |    | 0.5dB     |     | 0.5dB     |      | 0.5dB     |

|     |        | D30 | Transmit    | D5 | Transmit  | D84 | Transmit  | D111 | Transmit  |

|     |        |     | Attenuatio  | 7  | Attenuat  |     | Attenuat  |      | Attenuat  |

|     |        |     | n Control   |    | ion       |     | ion       |      | ion       |

|     |        |     | Bit 1dB     |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 1dB   |     | Bit 1dB   |      | Bit 1dB   |

|     |        | D31 | Transmit    | D5 | Transmit  | D85 | Transmit  | D112 | Transmit  |

|     |        |     | Attenuatio  | 8  | Attenuat  |     | Attenuat  |      | Attenuat  |

|     |        |     | n Control   |    | ion       |     | ion       |      | ion       |

|     |        |     | Bit 2dB     |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 2dB   |     | Bit 2dB   |      | Bit 2dB   |

|     |        | D32 | Transmit    | D5 | Transmit  | D86 | Transmit  | D113 | Transmit  |

|     |        |     | Attenuatio  | 9  | Attenuat  |     | Attenuat  |      | Attenuat  |

|     |        |     | n Control   |    | ion       |     | ion       |      | ion       |

|     |        |     | Bit 4dB     |    | Control   |     | Control   |      | Control   |

|     |        |     |             |    | Bit 4dB   |     | Bit 4dB   |      | Bit 4dB   |

|     |        | D33 | Set to 0    | D6 | Set to 0  | D87 | Set to 0  | D114 | Set to 0  |

|     |        |     |             | 0  |           |     |           |      |           |

|     |        | D34 | Set to 0    | D6 | Set to 0  | D88 | Set to 0  | D115 | Set to 0  |

|     |        |     |             | 1  |           |     |           |      |           |

| D35 | Receive    | D6 | Receive  | D89 | Receive  | D116 | Receive  |

|-----|------------|----|----------|-----|----------|------|----------|

|     | Attenuatio | 2  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 0.5dB  |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit      |     | Bit      |      | Bit      |

|     |            |    | 0.5dB    |     | 0.5dB    |      | 0.5dB    |

| D36 | Receive    | D6 | Receive  | D90 | Receive  | D117 | Receive  |

|     | Attenuatio | 3  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 1dB    |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit 1dB  |     | Bit 1dB  |      | Bit 1dB  |

| D37 | Receive    | D6 | Receive  | D91 | Receive  | D118 | Receive  |

|     | Attenuatio | 4  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 2dB    |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit 2dB  |     | Bit 2dB  |      | Bit 2dB  |

| D38 | Receive    | D6 | Receive  | D92 | Receive  | D119 | Receive  |

|     | Attenuatio | 5  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 4dB    |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit 4dB  |     | Bit 4dB  |      | Bit 4dB  |

| D39 | Receive    | D6 | Receive  | D93 | Receive  | D120 | Receive  |

|     | Attenuatio | 6  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 8dB    |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit 8dB  |     | Bit 8dB  |      | Bit 8dB  |

| D40 | Receive    | D6 | Receive  | D94 | Receive  | D121 | Receive  |

|     | Attenuatio | 7  | Attenuat |     | Attenuat |      | Attenuat |

|     | n Control  |    | ion      |     | ion      |      | ion      |

|     | Bit 16dB   |    | Control  |     | Control  |      | Control  |

|     |            |    | Bit 16dB |     | Bit 16dB |      | Bit 16dB |

#### **Notes:**

- 1)The data bit D0 is first-in, first-out.

- 2)The amplitude-phase and attenuation control bits are active at high level, and the delay control bits are active at low level. The delay state is positive delay.

- 3)The transmit-receive control states are shown in the following table.

| TR1 | TR2        | Transmit<br>Enable Bit | Receive<br>Enable Bit | State          |  |  |

|-----|------------|------------------------|-----------------------|----------------|--|--|

| 1   | 0          | X                      | 1                     | Receive State  |  |  |

| 0   | 1          | 1                      | X                     | Transmit State |  |  |

|     | Load State |                        |                       |                |  |  |

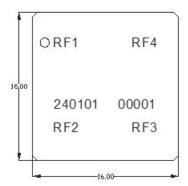

## Outline Dimensions and Pad Arrangement Diagram

The pad arrangement is shown in the following figure.

Note: Unmarked pins are GND.

| Serial | Symbol | Attribute | Level | Function Description |

|--------|--------|-----------|-------|----------------------|

| Number |        |           |       |                      |

| 1      | SEL   | Input            | TTL | Chip Select Signal, active at low level                                                                                         |  |

|--------|-------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|--|

| 2      | DOUT  | Output           | TTL | Serial output of the status register, self - test signal                                                                        |  |

| 3      | TRT   | Input            | TTL | Transmit external switch input                                                                                                  |  |

| 4      | TRR   | Input            | TTL | Receive external switch input                                                                                                   |  |

| 5      | SYN   | Input            | TTL | Write trigger signal for status data register 2, active at the rising edge                                                      |  |

| 6      | DARY  | Input            | TTL | Write trigger signal for status data register 1, active at the rising edge                                                      |  |

| 7      | CLK   | Input            | TTL | Clock signal input bit                                                                                                          |  |

| 8      | DATA  | Input            | TTL | Serial data input bit of the status register                                                                                    |  |

| 9      | OE    | Input            | TTL | Reset enable signal                                                                                                             |  |

| 10     | FIN   | Input            | TTL | Serial data input bit of the control register                                                                                   |  |

| 11     | FEN   | Input            | TTL | Serial input enable bit of the control register. Serial input is valid at low level, and FIN data is latched at the rising edge |  |

| 12     | -5V   | Input            |     | -5V voltage input                                                                                                               |  |

| 13     | -28V  | Input            |     | -28V voltage input                                                                                                              |  |

| 14     | +3.3V | Input            |     | +3.3V voltage input                                                                                                             |  |

| 15     | +28V  | Input            |     | +28V voltage input                                                                                                              |  |

| 16     | RF1   | Input/Ou<br>tput |     | Channel 1 RF input/output port                                                                                                  |  |

| 17     | RF2   | Input/Ou<br>tput |     | Channel 2 RF input/output port                                                                                                  |  |

| 18     | RF3   | Input/Ou<br>tput |     | Channel 3 RF input/output port                                                                                                  |  |

| 19     | RF4   | Input/Ou<br>tput |     | Channel 4 RF input/output port                                                                                                  |  |

| 20     | COM   | Input/Ou<br>tput |     | Common input/output port                                                                                                        |  |

| Others | GND   | Ground           |     | Ground                                                                                                                          |  |

#### **Precautions**

- 1. The module should be soldered to the board in a clean environment.

- 2. The bottom surface of the module is soldered with 400μm diameter high lead solder balls using a 183°C solder (Sn63Pb37).

- 3. The inside of the module can withstand a high temperature of 240°C. It is recommended to use Sn63Pb37 solder paste for SMT soldering of the module. After soldering, spray cleaning can be carried out, but ultrasonic cleaning is not allowed.

- 4. It is recommended to select a circuit board material with a small difference in thermal expansion coefficient from that of ceramics for the design of the circuit board on which the module is mounted. Infrared heating is not suitable for the repair of the module after it is mounted on the board.

- 5. There are electrostatic sensitive components inside the module. During transportation and storage, it is packaged in a special anti static sealed package. When soldering the module to the board, the personnel and equipment should have reliable anti static measures. Do not open the package without anti static measures. During the subsequent board level and system level testing and use of the module, electrostatic protection should be paid attention to.

- 6. The anti static sealed package of the module when shipped should be removed only when it is to be mounted and used. Unused modules after unpacking should be stored in a dry cabinet and mounted and used within 4 weeks.

- 7. When the module is in transmit operation, the heat dissipation is high. It is recommended to adopt a top cooling method.

- 8. There are DC blocking capacitors inside the RX1, RX2, RX3, RX4, TX1, TX2, TX3, TX4 ports, and there is also a DC blocking capacitor inside the COM port.

- 9. When designing the application circuit of the module,  $0.01\mu F$  and  $1\mu F$  ceramic filter capacitors should be connected in parallel to the ground near the +28V, +3.3V, and -5V pins of the module.

- 10. Since it is triggered by the rising edge, LD should be at a high level when there is no signal.

- 11. If there are any problems, please contact the marketing personnel in a timely manner.

- 12. The indicators described in this document are estimated values. The specific indicators shall be subject to actual measurement.